- 您现在的位置:买卖IC网 > Sheet目录1236 > PCI-EXP-T42G5-N1 (Lattice Semiconductor Corporation)IP CORE PCI EXPRESS ORCA 4

�� �

�

Lattice� Semiconductor�

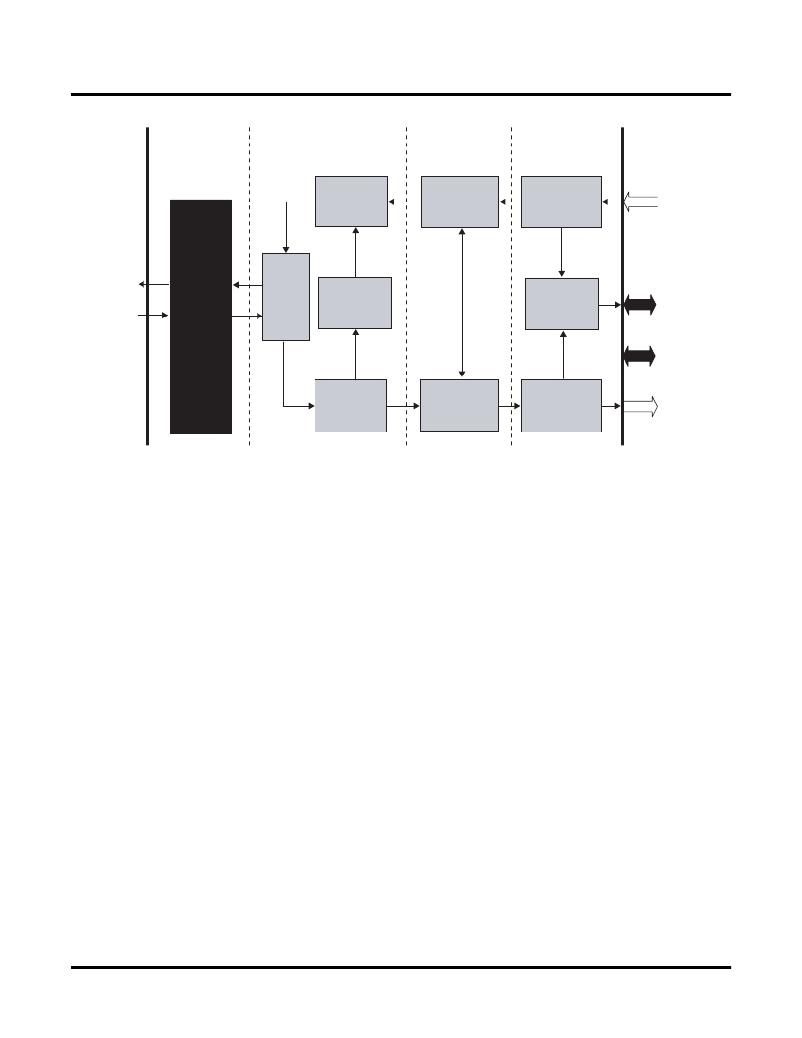

�Figure� 4.� Block� Diagram�

�PCI� Express� User’s� Guide�

�PHYSICAL� LAYER�

�Electrical� Block�

�PHYSICAL� LAYER�

�Logical� Block�

�DATA� LINK� LAYER�

�TRANSACTION� LAYER�

�Scrambler�

�and� Framer�

�TLP� and� DLLP�

�Transmission�

�Block�

�Transmit�

�User� Interface�

�Block�

�TX� USR�

�Interface�

�PCI�

�Express�

�Link�

�SERDES,�

�8b/10b�

�System� Bus�

�42G5�

�Interface�

�Link� Training�

�and�

�Configuration�

�Credit�

�Calculation�

�Block�

�Credit�

�Available�

�of�

�ORT42G5�

�Control�

�Status�

�Interface�

�Descrambler�

�and� Deframer�

�TLP� and� DLLP�

�Receive�

�Block�

�Receive�

�User� Interface�

�Block�

�RX� USR�

�Interface�

�Physical� Layer� Implementation�

�Electrical� Sub� Block�

�The� Electrical� sub� block� of� the� Physical� Layer� is� implemented� in� the� Embedded� logic� of� the� FPSC.� It� includes� one�

�channel� of� SERDES� and� also� 8b/10b� logic.�

�The� SERDES� circuitry� consists� of� a� receiver,� transmitter,� and� auxiliary� functional� blocks.� It� supports� serial� data� up�

�to� 3.7� Gbits/s.� 8b/10b� Decoder/Encoder� logic� follows� 8b/10b� transmission� code� as� de?ned� in� the� ANSI� X3.230-�

�1994� and� IEEE� 802.3z� speci?cations.�

�Refer� to� the� ORT42G5� and� ORT82G5� data� sheet� for� more� details� on� SERDES� and� 8b/10b� operation.�

�Logical� Sub� Block�

�The� Logical� sub� block� of� the� Physical� Layer� is� implemented� in� the� programmable� logic� portion� of� the� FPSC.� This�

�includes� the� Scrambler/De-scrambler,� Framer� /� De-Framer,� LTSSM� block� and� LWLSN� block.� These� blocks� are�

�described� below:�

�Scrambler/De-Scrambler�

�The� Scrambler/De-scrambler� function� is� implemented� using� Linear� Feedback� Shift� Registers.� This� is� performed� by�

�serially� XORing� the� 8-bit� character� with� the� 16-bit� output� of� the� LFSR.� The� ?nal� output� stage� of� the� LFSR� is� XORed�

�with� the� lower� bit� of� the� data� character� and� then� both� the� LFSR� and� data� register� are� serially� advanced.�

�The� LFSR� implements� the� polynomial:�

�G(S)� =� X� 16� +� X� 5� +� X� 4� =� X� 3� +� 1�

�Framer/De-Framer�

�The� Framer/De-Framer� implements� the� mechanism� which� uses� special� symbols� like� K28.2� (SDP)� to� start� a� DLLP,�

�K27.7� (STP)� to� start� a� TLP,� and� K29.7� (END)� to� mark� the� end� of� either� a� TLP� or� a� DLLP.� When� no� packet� informa-�

�tion� or� special� ordered-sets� are� being� transmitted,� the� transmitter� will� be� sending� idle� data.� The� idle� data� consists� of�

�the� data� byte� 0� (00h).� During� transmission� of� idle� data� the� skip� ordered� set� will� continue� to� be� transmitted.�

�5�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PCM18XH2

PROCESSOR MODULE MPLAB-ICE 2000

PCM18XN0

PROCESSOR MODULE FOR ICE2000

PDA-B-24-615-E-2B1-1-C

CIRCUIT BREAKER MAG 1P 15A

PFMF.260.2

PFMF PTC FUSE SMT 2.6A 1812

PFNF.200.2

PFNF PTC FUSE SMT 2A 1206

PFRY.375

PTC-FUSE RADIAL 72 VDC

PFSM.150.33.2

FUSE PTC 8A 15V FST-TRIP SMD

PFUF.150.2

FUSE PTC 3A 6V RESET SMD

相关代理商/技术参数

PCI-EXT+64U-

制造商:Twin Industries 功能描述:EXTENDER CARD, ACTIVE, BUS TYPE, 3.3 VOLTS TEST CARD,

PCI-G-EVB

功能描述:BOARD EVAL DISKONCHIP PCI-G RoHS:否 类别:编程器,开发系统 >> 过时/停产零件编号 系列:mDOC/mModule 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

PCIH-10-6P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 6 POS SLDR ST PNL MNT 6TERM - Bulk

PCIH-10-98P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 6 POS SLDR ST PNL MNT 6TERM - Bulk

PCIH-12-10P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 10 POS SLDR ST PNL MNT 10TERM - Bulk

PCIH-12-8P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 8 POS SLDR ST PNL MNT 8TERM - Bulk

PCIH-14-12P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 12 POS SLDR ST PNL MNT 12TERM - Bulk

PCIH-14-19P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 19 POS SLDR ST PNL MNT 19TERM - Bulk